We've just updated MediaWiki and its underlying software. If anything doesn't look or work quite right, please mention it to us. --RanAS

ROR (SPC700): Difference between revisions

From SnesLab

(improve description) |

(9 bits rotated) |

||

| (13 intermediate revisions by the same user not shown) | |||

| Line 7: | Line 7: | ||

|'''Speed''' | |'''Speed''' | ||

|+ | |+ | ||

| | |[[Accumulator Addressing | Accumulator]] | ||

|7C | |7C | ||

|1 byte | |1 byte | ||

|2 cycles | |2 cycles | ||

|+ | |+ | ||

| | |[[Direct Page Addressing | Direct Page]] | ||

|6B | |6B | ||

|2 bytes | |2 bytes | ||

|4 cycles | |4 cycles | ||

|+ | |+ | ||

| | |[[Direct Page Indexed by X]] | ||

|7B | |7B | ||

|2 bytes | |2 bytes | ||

|5 cycles | |5 cycles | ||

|+ | |+ | ||

| | |[[Absolute Addressing | Absolute]] | ||

|6C | |6C | ||

|3 bytes | |3 bytes | ||

| Line 29: | Line 29: | ||

{| class="wikitable" style="float:right;clear:right;width:30%" | {| class="wikitable" style="float:right;clear:right;width:30%" | ||

!colspan="8"|Flags | !colspan="8"|Flags Affected | ||

|+ | |||

|[[Negative Flag|N]] | |||

|[[Overflow Flag|V]] | |||

|[[Direct Page Flag|P]] | |||

|[[Break Flag|B]] | |||

|[[Half-Carry Flag|H]] | |||

|[[Interrupt Enable Flag|I]] | |||

|[[Zero Flag|Z]] | |||

|[[Carry Flag|C]] | |||

|+ | |+ | ||

|N | |N | ||

|. | |. | ||

|. | |. | ||

| Line 46: | Line 46: | ||

|. | |. | ||

|. | |. | ||

| | |Z | ||

| | |C | ||

|} | |} | ||

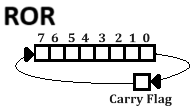

'''ROR''' is an [[SPC700]] instruction that rotates its operand one bit to the right. The old value of the [[carry flag]] is rotated into the most significant bit. The least significant bit is rotated into the carry flag. | '''ROR''' is an [[SPC700]] instruction that rotates every bit of its operand one bit to the right. The old value of the [[carry flag]] is rotated into the most significant bit. The least significant bit is rotated into the carry flag. A total of 9 bits are rotated. | ||

The official manual has the bit shift operators for ROR pointing the wrong way. | |||

==== Syntax ==== | |||

<pre> | |||

ROR A | |||

ROR dp | |||

ROR dp+X | |||

ROR !abs | |||

</pre> | |||

[[File:ror.png]] | |||

=== See Also === | === See Also === | ||

* [[ROL (SPC700)]] | * [[ROL (SPC700)]] | ||

* [[LSR (SPC700)]] | |||

* [[ROR]] | * [[ROR]] | ||

* [[ROR (Super FX)]] | |||

=== External Links === | === External Links === | ||

* Official Super Nintendo development manual on ROR: [https://archive.org/details/SNESDevManual/book1/page/n232 Appendix C-7 of Book I] | * Official Super Nintendo development manual on ROR: [https://archive.org/details/SNESDevManual/book1/page/n232 Appendix C-7 of Book I] | ||

* anomie: https://github.com/yupferris/TasmShiz/blob/master/spc700.txt#L554 | |||

[[Category:ASM]] | [[Category:ASM]] | ||

[[Category:SPC700]] | [[Category:SPC700]] | ||

[[Category:Shift Rotation Commands]] | [[Category:Shift Rotation Commands]] | ||

Latest revision as of 19:34, 4 August 2024

| Basic Info | |||||||

|---|---|---|---|---|---|---|---|

| Addressing Mode | Opcode | Length | Speed | ||||

| Accumulator | 7C | 1 byte | 2 cycles | ||||

| Direct Page | 6B | 2 bytes | 4 cycles | ||||

| Direct Page Indexed by X | 7B | 2 bytes | 5 cycles | ||||

| Absolute | 6C | 3 bytes | 5 cycles | ||||

| Flags Affected | |||||||

|---|---|---|---|---|---|---|---|

| N | V | P | B | H | I | Z | C |

| N | . | . | . | . | . | Z | C |

ROR is an SPC700 instruction that rotates every bit of its operand one bit to the right. The old value of the carry flag is rotated into the most significant bit. The least significant bit is rotated into the carry flag. A total of 9 bits are rotated.

The official manual has the bit shift operators for ROR pointing the wrong way.

Syntax

ROR A ROR dp ROR dp+X ROR !abs

See Also

External Links

- Official Super Nintendo development manual on ROR: Appendix C-7 of Book I

- anomie: https://github.com/yupferris/TasmShiz/blob/master/spc700.txt#L554