We've just updated MediaWiki and its underlying software. If anything doesn't look or work quite right, please mention it to us. --RanAS

Left Right Clock: Difference between revisions

From SnesLab

(added audio category) |

(header-ed references, more info on what channels) |

||

| Line 1: | Line 1: | ||

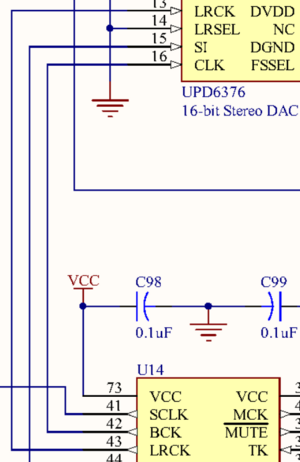

The '''Left Right Clock''' controls stereo processing. The rising and falling edges of this clock tell when one channel begins and the other stops. It is denoted '''LRCK''', and connected to pin 13 of the 16-bit [[Stereo DAC]] and pin 43 of the [[Sony S-DSP]] sound chip. | The '''Left Right Clock''' controls stereo processing. The rising and falling edges of this clock tell when processing for one stereo channel begins and the other stops. It is denoted '''LRCK''', and connected to pin 13 of the 16-bit [[Stereo DAC]] and pin 43 of the [[Sony S-DSP]] sound chip. | ||

[[File:lrck schematic.png|thumb|The left right clock is in region C4 of the jwdonal schematic]] | [[File:lrck schematic.png|thumb|The left right clock is in region C4 of the jwdonal schematic]] | ||

References | === References === | ||

* https://forums.nesdev.org/viewtopic.php?p=285045#p285045 | * https://forums.nesdev.org/viewtopic.php?p=285045#p285045 | ||

Revision as of 07:49, 14 May 2023

The Left Right Clock controls stereo processing. The rising and falling edges of this clock tell when processing for one stereo channel begins and the other stops. It is denoted LRCK, and connected to pin 13 of the 16-bit Stereo DAC and pin 43 of the Sony S-DSP sound chip.