We've just updated MediaWiki and its underlying software. If anything doesn't look or work quite right, please mention it to us. --RanAS

FastROM: Difference between revisions

From SnesLab

(→See Also: 420Dh) |

(added ROM access speed) |

||

| Line 1: | Line 1: | ||

'''FastROM''' is 3.58 MHz. It is about 33% faster than [[SlowROM]]. FastROM is a property of the ROM chip itself and not the board it is soldered onto.<sup>[2]</sup> When the [[5A22]] is operating at fastROM speed, there are 6 [[master clock]] cycles per CPU [[machine cycles]]. | '''FastROM''' is 3.58 MHz and its ROM access speed is 120ns. It is about 33% faster than [[SlowROM]]. FastROM is a property of the ROM chip itself and not the board it is soldered onto.<sup>[2]</sup> When the [[5A22]] is operating at fastROM speed, there are 6 [[master clock]] cycles per CPU [[machine cycles]]. | ||

FastROM speeds only apply to the upper halves of banks $80-bf and all of banks $c0-ff.<sup>[1]</sup> | FastROM speeds only apply to the upper halves of banks $80-bf and all of banks $c0-ff.<sup>[1]</sup> | ||

Latest revision as of 17:08, 19 August 2024

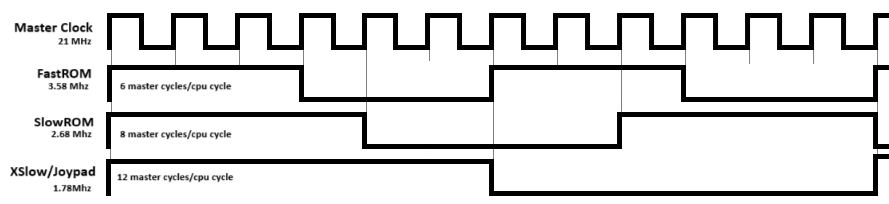

FastROM is 3.58 MHz and its ROM access speed is 120ns. It is about 33% faster than SlowROM. FastROM is a property of the ROM chip itself and not the board it is soldered onto.[2] When the 5A22 is operating at fastROM speed, there are 6 master clock cycles per CPU machine cycles.

FastROM speeds only apply to the upper halves of banks $80-bf and all of banks $c0-ff.[1]

The SAS cannot use FastROM.[3] Games which utilize fastrom should indicate this at bit 4 of FFD5 of the cartridge header.[4]

See Also

External Links

- https://gbatemp.net/threads/romhacker-kandowontu-converts-more-than-80-snes-titles-into-fastrom-improving-their-performance.629133

- "High Speed Required?" checkbox on page 1-2-9 of Book I of the official Super Nintendo development manual

References

- Near, https://forums.nesdev.org/viewtopic.php?t=9585

- Bregalad, lbid.

- caution 3.3.6.1 on page 1-3-4 of Book II of the official Super Nintendo development manual

- http://problemkaputt.de/fullsnes.htm#snesmemorycontrol