We've just updated MediaWiki and its underlying software. If anything doesn't look or work quite right, please mention it to us. --RanAS

XCE: Difference between revisions

From SnesLab

(→Syntax: B unaffected) |

(→Syntax: clarify that there are two index regs) |

||

| Line 49: | Line 49: | ||

</pre> | </pre> | ||

The low bytes of | The low bytes of both index registers are unaffected by a mode change. The high byte B of the accumulator is also unaffected. | ||

==== Examples ==== | ==== Examples ==== | ||

Revision as of 14:19, 24 July 2024

| Basic Info | |||||||

|---|---|---|---|---|---|---|---|

| Addressing Mode | Opcode | Length | Speed | ||||

| Implied (type 2) | FB | 1 byte | 2 cycles | ||||

| Flags Affected | ||||||||

|---|---|---|---|---|---|---|---|---|

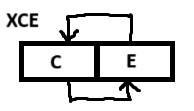

| N | V | M | X | D | I | Z | C | E |

| . | . | . | . | . | E | C | ||

XCE is a 65c816 instruction that exchanges the carry and emulation bits. It typically appears soon after the Reset Vector following a CLC, to switch the S-CPU into 65c816 native mode. The carry flag was chosen because:

- it is easy to set and clear

- it is used less frequently than the negative and zero flags

- it can be tested with BCC and BCS

Syntax

XCE

The low bytes of both index registers are unaffected by a mode change. The high byte B of the accumulator is also unaffected.

Examples

Switching to native mode:

CLC XCE

Switching to emulation mode:

SEC XCE

See Also

External Links

- Eyes & Lichty page 525, on XCE: https://archive.org/details/0893037893ProgrammingThe65816/page/525

- "Exchanges" on page 102, lbid: https://archive.org/details/0893037893ProgrammingThe65816/page/102

- Labiak page 205 on XCE: https://archive.org/details/Programming_the_65816/page/n215

- snes9x implementation of XCE: https://github.com/snes9xgit/snes9x/blob/master/cpuops.cpp#L2517

- undisbeliever on XCE: https://undisbeliever.net/snesdev/65816-opcodes.html#xce-exchange-carry-and-emulation-bits

- Clark, Bruce. http://www.6502.org/tutorials/65c816opcodes.html#6.10.4