We've just updated MediaWiki and its underlying software. If anything doesn't look or work quite right, please mention it to us. --RanAS

LSR (Super FX): Difference between revisions

From SnesLab

(made flags affected more prominent) |

(→See Also: fixed ROL link) |

||

| Line 65: | Line 65: | ||

* [[LSR (SPC700)]] | * [[LSR (SPC700)]] | ||

* [[ROR (Super FX)]] | * [[ROR (Super FX)]] | ||

* [[ | * [[ROL (Super FX)]] | ||

* [[ROR]] | * [[ROR]] | ||

Latest revision as of 02:01, 22 August 2024

| Basic Info | |||||||

|---|---|---|---|---|---|---|---|

| Addressing Mode | Opcode | Length | ROM Speed | RAM Speed | Cache Speed | ||

| Implied (type 1) | 03 | 1 byte | 3 cycles | 3 cycles | 1 cycle | ||

| Flags Affected | ||||||||

|---|---|---|---|---|---|---|---|---|

| B | ALT1 | ALT2 | O/V | S | CY | Z | ||

| 0 | 0 | 0 | . | 0 | CY | Z | ||

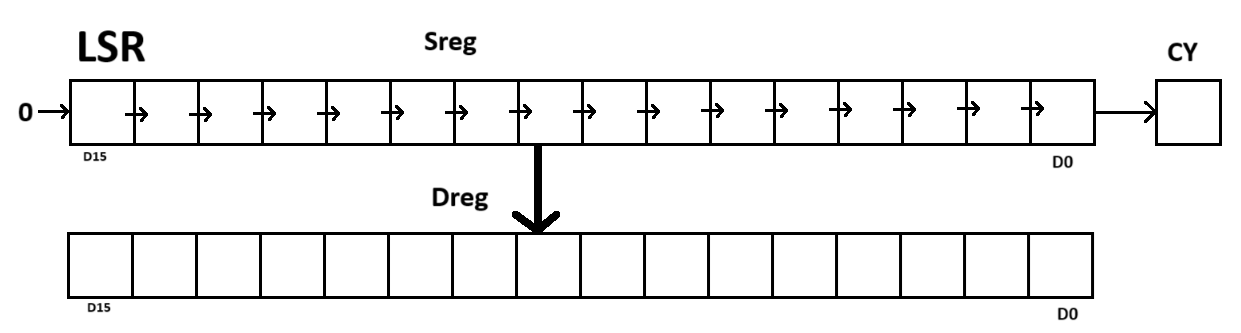

LSR (Logical Shift Right) is a Super FX instruction that shifts all bits of the source register's value to the right one bit while shifting a zero into the most significant bit, storing the result in the destination register. Bit 0 is shifted into CY. The source register itself is left unchanged.

The ALT0 state is restored.

The source and destination registers should be specified in advance using WITH, FROM, or TO. Otherwise, R0 serves as the default.

Syntax

LSR

Example

Let:

Sreg : R8 Dreg : R0 R8 = b53fh (1011 0101 0011 1111b)

After executing LSR:

R0 = 5a9fh (0101 1010 1001 1111b) CY = 1

See Also

External Links

- Official Nintendo documentation on LSR: 9.55 on page 2-9-78 of Book II