We've just updated MediaWiki and its underlying software. If anything doesn't look or work quite right, please mention it to us. --RanAS

ROR (Super FX): Difference between revisions

From SnesLab

(→External Links: 9.76) |

(of the 3 types of implied 1 is the closest) |

||

| Line 1: | Line 1: | ||

{| class="wikitable" style="float:right;clear:right;width: | {| class="wikitable" style="float:right;clear:right;width:50%" | ||

!colspan="8"|Basic Info | !colspan="8"|Basic Info | ||

|+ | |+ | ||

|'''Addressing Mode''' | |||

|'''Opcode''' | |'''Opcode''' | ||

|'''Length''' | |'''Length''' | ||

| Line 8: | Line 9: | ||

|'''Cache Speed''' | |'''Cache Speed''' | ||

|+ | |+ | ||

|[[Implied]] (type 1) | |||

|97 | |97 | ||

|1 byte | |1 byte | ||

Revision as of 19:50, 2 July 2024

| Basic Info | |||||||

|---|---|---|---|---|---|---|---|

| Addressing Mode | Opcode | Length | ROM Speed | RAM Speed | Cache Speed | ||

| Implied (type 1) | 97 | 1 byte | 3 cycles | 3 cycles | 1 cycle | ||

| Flags Affected | ||||||||

|---|---|---|---|---|---|---|---|---|

| B | ALT1 | ALT2 | O/V | S | CY | Z | ||

| 0 | 0 | 0 | . | |||||

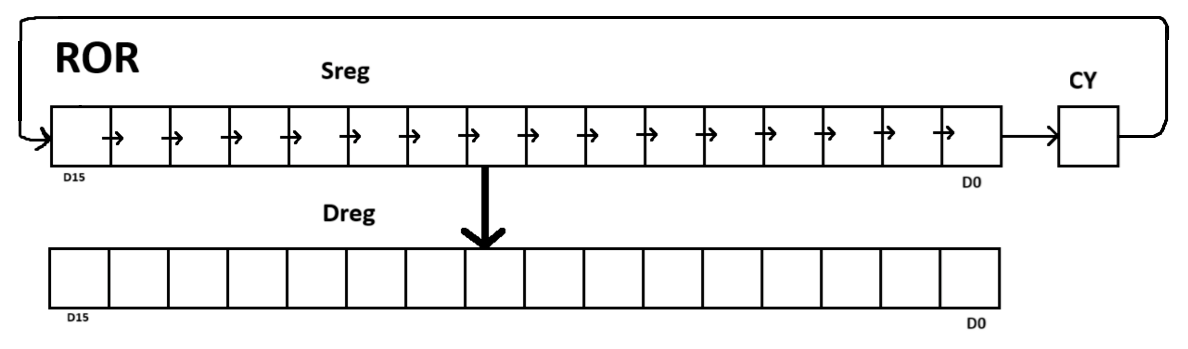

ROR (Rotate Right) is a Super FX instruction that rotates the source register and carry flag one bit to the right into the destination register. Bit 0 of Sreg is shifted into the carry flag.

See Also

External Links

- Official Nintendo documentation on ROR: 9.76 on page 2-9-105 of Book II

- example: page 2-9-106, lbid.