Direct Page: Difference between revisions

(added image) |

(more specific) |

||

| Line 2: | Line 2: | ||

It is technically, as its namesake, the 256 bytes accessible via '''Direct Page Addressing''', and has special handling of wrapping behavior. | It is technically, as its namesake, the 256 bytes accessible via '''Direct Page Addressing''', and has special handling of wrapping behavior. | ||

Colloquial usage of this term will invariably refer to the '''Direct Page Register''' itself and by extension the group of Direct addressing modes it affects, due to the other addressing modes not being limited to 256 bytes. | Colloquial usage of this term will invariably refer to the '''Direct Page Register''' itself and by extension the group of Direct addressing modes it affects, due to the other addressing modes not being limited to 256 bytes. | ||

The wrapping behavior will ''always'' confine it to Bank 0, but if in emulation | The wrapping behavior will ''always'' confine it to Bank 0, but if in [[emulation mode]] will also confine it to the [[zeropage]] when DL is zero. | ||

The direct page may overlap the [[stack]].<sup>[4]</sup> | The direct page may overlap the [[stack]].<sup>[4]</sup> | ||

Revision as of 22:52, 22 July 2024

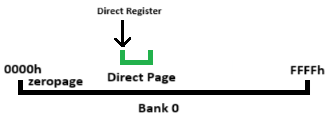

The Direct Page is much like the zeropage on the 6502, but can be moved around to anywhere within the first 64K bank. It is technically, as its namesake, the 256 bytes accessible via Direct Page Addressing, and has special handling of wrapping behavior. Colloquial usage of this term will invariably refer to the Direct Page Register itself and by extension the group of Direct addressing modes it affects, due to the other addressing modes not being limited to 256 bytes. The wrapping behavior will always confine it to Bank 0, but if in emulation mode will also confine it to the zeropage when DL is zero.

The direct page may overlap the stack.[4]

On the SPC700, the direct page can only be in one of two places: either coincident with page zero or page one.