BRK

| Basic Info | |||||||

|---|---|---|---|---|---|---|---|

| Addressing Mode | Opcode | Length | Speed | ||||

| Stack (Interrupt) | 00 | 2 bytes | 8 cycles* | ||||

| Flags Affected | ||||||||

|---|---|---|---|---|---|---|---|---|

| N | V | M | X / B | D | I | Z | C | |

| 65c816 native mode | . | . | . | . | 0 | 1 | . | . |

| 6502 emulation mode | . | . | . | 1 | 0 | 1 | . | . |

BRK (Break) is a 65x instruction that triggers a software interrupt. The byte following the opcode is called the signature byte. The state of the interrupt disable flag has no effect on the behavior of BRK although it will be set after BRK runs. In other words, BRK causes an NMI.

Control is routed to the BRK handler, whose address is stored at the BRK vector:

- In native mode, this vector is at $00:FFE6.

- In emulation mode, this vector is at $FFFE.

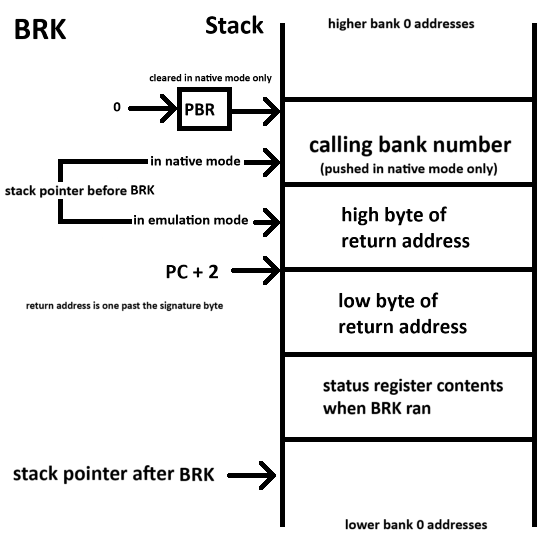

The PBR is cleared, but in native mode its previous value is pushed to the stack.

Syntax

BRK BRK sig

Cycle Skipped

BRK takes one fewer cycle in emulation mode as it doesn't need to push the program counter bank register to the stack.

If the signature byte was omitted from the assembler source, then it ends up serving double duty as the opcode of the next instruction. In this case the interrupt handler must decrement the return address on the stack so that the eventual RTI does not cause derailment.

BRK used to be considered a one-byte instruction in an early datasheet.

See Also

External Links

- Eyes & Lichty, page 436 on BRK

- Figure 13.3, Break Signature Byte Illustration, lbid, page 256

- Labiak, page 126 on BRK

- 9.11 on MCS6500 Manual, page 144 on BRK

- Carr, page 252 on BRK

- Leventhal, page 3-49 on BRK

- snes9x implementation of BRK: https://github.com/snes9xgit/snes9x/blob/master/cpuops.cpp#L2547

- Pickens, John. http://www.6502.org/tutorials/6502opcodes.html#BRK

- https://undisbeliever.net/snesdev/65816-opcodes.html#software-interrupts