We've just updated MediaWiki and its underlying software. If anything doesn't look or work quite right, please mention it to us. --RanAS

ROL: Difference between revisions

From SnesLab

(added group 2 category) |

(→See Also: spc700) |

||

| (28 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

{| class="wikitable" style="float:right;clear:right;width:40%" | |||

{| class="wikitable" style="float:right;clear:right;width: | |||

!colspan="8"|Basic Info | !colspan="8"|Basic Info | ||

|+ | |+ | ||

| Line 9: | Line 7: | ||

|'''Speed''' | |'''Speed''' | ||

|+ | |+ | ||

| | |[[Accumulator Addressing|Accumulator]] | ||

|2A | |2A | ||

|1 byte | |1 byte | ||

|2 cycles | |2 cycles | ||

|+ | |+ | ||

| | |[[Absolute]] | ||

|2E | |2E | ||

|3 bytes | |3 bytes | ||

|6 cycles | |6 cycles* | ||

|+ | |+ | ||

| | |[[Direct Page Addressing|Direct Page]] | ||

|26 | |26 | ||

|2 bytes | |2 bytes | ||

|5 cycles | |5 cycles* | ||

|+ | |+ | ||

|absolute indexed by X | |absolute indexed by X | ||

|3E | |3E | ||

|3 bytes | |3 bytes | ||

|7 cycles | |7 cycles* | ||

|+ | |+ | ||

|direct page indexed by X | |direct page indexed by X | ||

|36 | |36 | ||

|2 bytes | |2 bytes | ||

|6 cycles | |6 cycles* | ||

|} | |} | ||

{| class="wikitable" style="float:right;clear:right;width:30%" | {| class="wikitable" style="float:right;clear:right;width:30%" | ||

!colspan="9"|Flags | !colspan="9"|Flags Affected | ||

|+ | |+ | ||

|N | |[[N Flag|N]] | ||

|V | |[[V Flag|V]] | ||

|M | |[[M Flag|M]] | ||

|X | |[[X Flag|X]] | ||

|D | |[[D Flag|D]] | ||

|I | |[[I Flag|I]] | ||

|Z | |[[Z Flag|Z]] | ||

|C | |[[C Flag|C]] | ||

|+ | |+ | ||

| | | | ||

| Line 56: | Line 54: | ||

| | | | ||

|} | |} | ||

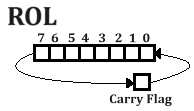

'''ROL''' (Rotate Left) is a 65x instruction that rotates a value and the [[carry flag]] left one bit. The most significant bit is shifted into the carry flag. The carry flag is shifted into the least significant bit. | |||

===== Cycle Penalties ===== | |||

* Except in [[accumulator addressing]], ROL takes two extra cycles when the accumulator is 16 bits wide. | |||

* In [[direct page addressing]] modes, ROL takes another extra cycle if the low byte of the [[direct page register]] is nonzero. | |||

[[File:rol.png]] | |||

=== See Also === | === See Also === | ||

* [[ROR]] | * [[ROR]] | ||

* [[ROL (SPC700)]] | |||

* [[ROL (Super FX)]] | |||

=== External Links === | |||

* [[Eyes & Lichty]] page 490, on ROL: https://archive.org/details/0893037893ProgrammingThe65816/page/n516 | |||

* lbid page 190 before & after diagram of ROL: https://archive.org/details/0893037893ProgrammingThe65816/page/n216 | |||

* [[Labiak]] page 174 on ROL: https://archive.org/details/Programming_the_65816/page/n184 | |||

* [[MCS6500 Manual]] page 149 on ROL: https://archive.org/details/mos_microcomputers_programming_manual/page/n170 | |||

* [[Carr]] page 269 on ROL: https://archive.org/details/6502UsersManual/page/n282 | |||

* [[Leventhal]] page 3-85 on ROL: https://archive.org/details/6502-assembly-language-programming/page/n134 | |||

* snes9x implementation of ROL: https://github.com/snes9xgit/snes9x/blob/master/cpuops.cpp#L1011 | |||

* undisbeliever on ROL: https://undisbeliever.net/snesdev/65816-opcodes.html#rol-rotate-left | |||

[[Category:ASM]] | [[Category:ASM]] | ||

[[Category:Group Two Instructions]] | [[Category:Group Two Instructions]] | ||

[[Category:Read-Modify-Write Instructions]] | |||

[[Category:Inherited from 6502]] | |||

Latest revision as of 19:24, 8 January 2024

| Basic Info | |||||||

|---|---|---|---|---|---|---|---|

| Addressing Mode | Opcode | Length | Speed | ||||

| Accumulator | 2A | 1 byte | 2 cycles | ||||

| Absolute | 2E | 3 bytes | 6 cycles* | ||||

| Direct Page | 26 | 2 bytes | 5 cycles* | ||||

| absolute indexed by X | 3E | 3 bytes | 7 cycles* | ||||

| direct page indexed by X | 36 | 2 bytes | 6 cycles* | ||||

| Flags Affected | ||||||||

|---|---|---|---|---|---|---|---|---|

| N | V | M | X | D | I | Z | C | |

| . | . | . | . | . | ||||

ROL (Rotate Left) is a 65x instruction that rotates a value and the carry flag left one bit. The most significant bit is shifted into the carry flag. The carry flag is shifted into the least significant bit.

Cycle Penalties

- Except in accumulator addressing, ROL takes two extra cycles when the accumulator is 16 bits wide.

- In direct page addressing modes, ROL takes another extra cycle if the low byte of the direct page register is nonzero.

See Also

External Links

- Eyes & Lichty page 490, on ROL: https://archive.org/details/0893037893ProgrammingThe65816/page/n516

- lbid page 190 before & after diagram of ROL: https://archive.org/details/0893037893ProgrammingThe65816/page/n216

- Labiak page 174 on ROL: https://archive.org/details/Programming_the_65816/page/n184

- MCS6500 Manual page 149 on ROL: https://archive.org/details/mos_microcomputers_programming_manual/page/n170

- Carr page 269 on ROL: https://archive.org/details/6502UsersManual/page/n282

- Leventhal page 3-85 on ROL: https://archive.org/details/6502-assembly-language-programming/page/n134

- snes9x implementation of ROL: https://github.com/snes9xgit/snes9x/blob/master/cpuops.cpp#L1011

- undisbeliever on ROL: https://undisbeliever.net/snesdev/65816-opcodes.html#rol-rotate-left