We've just updated MediaWiki and its underlying software. If anything doesn't look or work quite right, please mention it to us. --RanAS

LSR (SPC700): Difference between revisions

From SnesLab

(see also ASL) |

(how many bits is operand) |

||

| (18 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

{| class="wikitable" style="float:right;clear:right;width:40%" | |||

{| class="wikitable" style="float:right;clear:right;width: | |||

!colspan="8"|Basic Info | !colspan="8"|Basic Info | ||

|+ | |+ | ||

| Line 9: | Line 7: | ||

|'''Speed''' | |'''Speed''' | ||

|+ | |+ | ||

| | |[[Accumulator Addressing | Accumulator]] | ||

|5C | |5C | ||

|1 byte | |1 byte | ||

|2 cycles | |2 cycles | ||

|+ | |+ | ||

| | |[[Direct Page Addressing | Direct Page]] | ||

|4B | |4B | ||

|2 bytes | |2 bytes | ||

|4 cycles | |4 cycles | ||

|+ | |+ | ||

| | |[[Direct Page Indexed by X]] | ||

|5B | |5B | ||

|2 bytes | |2 bytes | ||

|5 cycles | |5 cycles | ||

|+ | |+ | ||

| | |[[Absolute Addressing | Absolute]] | ||

|4C | |4C | ||

|3 bytes | |3 bytes | ||

| Line 31: | Line 29: | ||

{| class="wikitable" style="float:right;clear:right;width:30%" | {| class="wikitable" style="float:right;clear:right;width:30%" | ||

!colspan="8"|Flags | !colspan="8"|Flags Affected | ||

|+ | |||

|[[Negative Flag|N]] | |||

|[[Overflow Flag|V]] | |||

|[[Direct Page Flag|P]] | |||

|[[Break Flag|B]] | |||

|[[Half-Carry Flag|H]] | |||

|[[Interrupt Enable Flag|I]] | |||

|[[Zero Flag|Z]] | |||

|[[Carry Flag|C]] | |||

|+ | |+ | ||

|N | |N | ||

|. | |. | ||

|. | |. | ||

| Line 48: | Line 46: | ||

|. | |. | ||

|. | |. | ||

| | |Z | ||

| | |C | ||

|} | |} | ||

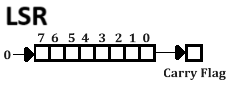

'''LSR''' (Logical Shift Right) is an [[SPC700]] instruction that shifts all 8 bits of its operand one bit to the right, dividing it by two. The least significant bit is shifted into the [[carry flag]]. A zero is shifted into the most significant bit. | |||

The official manual has the bit shift operators for LSR pointing the wrong way. | |||

==== Syntax ==== | |||

<pre> | |||

LSR A | |||

LSR dp | |||

LSR dp+X | |||

LSR !abs | |||

</pre> | |||

[[File:lsr_spc.png]] | |||

LSR is a fast alternative to [[DIV]] when dividing by a power of two. | |||

=== See Also === | === See Also === | ||

* [[ASL (SPC700)]] | * [[ASL (SPC700)]] | ||

* [[LSR]] | |||

=== External Links === | === External Links === | ||

* Official Super Nintendo development manual on LSR: [https://archive.org/details/SNESDevManual/book1/page/n232 Appendix C-7 of Book I] | * Official Super Nintendo development manual on LSR: [https://archive.org/details/SNESDevManual/book1/page/n232 Appendix C-7 of Book I] | ||

* anomie: https://github.com/yupferris/TasmShiz/blob/master/spc700.txt#L457 | |||

[[Category:ASM]] | [[Category:ASM]] | ||

[[Category:SPC700]] | [[Category:SPC700]] | ||

[[Category:Shift Rotation Commands]] | [[Category:Shift Rotation Commands]] | ||

Latest revision as of 00:04, 15 August 2024

| Basic Info | |||||||

|---|---|---|---|---|---|---|---|

| Addressing Mode | Opcode | Length | Speed | ||||

| Accumulator | 5C | 1 byte | 2 cycles | ||||

| Direct Page | 4B | 2 bytes | 4 cycles | ||||

| Direct Page Indexed by X | 5B | 2 bytes | 5 cycles | ||||

| Absolute | 4C | 3 bytes | 5 cycles | ||||

| Flags Affected | |||||||

|---|---|---|---|---|---|---|---|

| N | V | P | B | H | I | Z | C |

| N | . | . | . | . | . | Z | C |

LSR (Logical Shift Right) is an SPC700 instruction that shifts all 8 bits of its operand one bit to the right, dividing it by two. The least significant bit is shifted into the carry flag. A zero is shifted into the most significant bit.

The official manual has the bit shift operators for LSR pointing the wrong way.

Syntax

LSR A LSR dp LSR dp+X LSR !abs

LSR is a fast alternative to DIV when dividing by a power of two.

See Also

External Links

- Official Super Nintendo development manual on LSR: Appendix C-7 of Book I

- anomie: https://github.com/yupferris/TasmShiz/blob/master/spc700.txt#L457