We've just updated MediaWiki and its underlying software. If anything doesn't look or work quite right, please mention it to us. --RanAS

LSR: Difference between revisions

From SnesLab

(linkify admode) |

(→Cycle Penalties: deindented) |

||

| (23 intermediate revisions by the same user not shown) | |||

| Line 51: | Line 51: | ||

|. | |. | ||

|. | |. | ||

| | |Z | ||

| | |C | ||

|} | |} | ||

'''LSR''' (Logical Shift Right) is a 65x instruction that shifts a value one bit to the right (division by two). The most significant bit | '''LSR''' (Logical Shift Right) is a 65x instruction that shifts every bit of a value one bit to the right (division by two). The most significant bit and [[negative flag]] are cleared. The least significant bit is shifted into the [[carry flag]]. The previous value of the carry flag is lost (unlike with [[ROR]]). | ||

===== Cycle Penalties | The size of the accumulator determines how many bits are shifted (8 or 16) not including the clearing zero and carry flag. | ||

==== Syntax ==== | |||

<pre> | |||

LSR | |||

LSR A | |||

LSR addr | |||

LSR dp | |||

LSR addr, X | |||

LSR dp, X | |||

</pre> | |||

==== Cycle Penalties ==== | |||

* Except in [[accumulator addressing]], LSR takes an extra two cycles when the accumulator is 16 bits wide | * Except in [[accumulator addressing]], LSR takes an extra two cycles when the accumulator is 16 bits wide | ||

* In [[direct page addressing]] modes, LSR takes another extra cycle if the low byte of the [[direct page register]] is nonzero. | * In [[direct page addressing]] modes, LSR takes another extra cycle if the low byte of the [[direct page register]] is nonzero. | ||

[[File:816_lsr.png]] | |||

=== See Also === | === See Also === | ||

| Line 65: | Line 79: | ||

* [[LSR (SPC700)]] | * [[LSR (SPC700)]] | ||

* [[LSR (Super FX)]] | * [[LSR (Super FX)]] | ||

* [[DIV2]] | |||

=== External Links === | === External Links === | ||

* [[Eyes & Lichty]] page 465 | * [[Eyes & Lichty]], [https://archive.org/details/0893037893ProgrammingThe65816/page/465 page 465] on LSR | ||

* [[Labiak]] | * lbid [https://archive.org/details/0893037893ProgrammingThe65816/page/191 page 191], before & after diagram of LSR | ||

* [[MCS6500 Manual]] | * [[Labiak]], [https://archive.org/details/Programming_the_65816/page/n162 page 152] on LSR | ||

* [[Carr]] | * 10.1 on [[MCS6500 Manual]], [https://archive.org/details/mos_microcomputers_programming_manual/page/n169 page 148] on LSR | ||

* [[Leventhal]] | * [[Carr]], [https://archive.org/details/6502UsersManual/page/n278 page 265] on LSR | ||

* [[Leventhal]], [https://archive.org/details/6502-assembly-language-programming/page/n125 page 3-76] on LSR | |||

* snes9x implementation of LSR: https://github.com/snes9xgit/snes9x/blob/master/cpuops.cpp#L862 | * snes9x implementation of LSR: https://github.com/snes9xgit/snes9x/blob/master/cpuops.cpp#L862 | ||

* undisbeliever on LSR: https://undisbeliever.net/snesdev/65816-opcodes.html#lsr-logical-shift-right | * undisbeliever on LSR: https://undisbeliever.net/snesdev/65816-opcodes.html#lsr-logical-shift-right | ||

* Pickens, John. http://www.6502.org/tutorials/6502opcodes.html#LSR | |||

* Clark, Bruce. http://www.6502.org/tutorials/65c816opcodes.html#6.1.3 | |||

[[Category:ASM]] | [[Category:ASM]] | ||

Latest revision as of 17:45, 23 August 2024

| Basic Info | |||||||

|---|---|---|---|---|---|---|---|

| Addressing Mode | Opcode | Length | Speed | ||||

| Accumulator | 4A | 1 byte | 2 cycles | ||||

| Absolute | 4E | 3 bytes | 6 cycles* | ||||

| Direct Page | 46 | 2 bytes | 5 cycles* | ||||

| Absolute Indexed by X | 5E | 3 bytes | 7 cycles* | ||||

| Direct Page Indexed by X | 56 | 2 bytes | 6 cycles* | ||||

| Flags Affected | ||||||||

|---|---|---|---|---|---|---|---|---|

| N | V | M | X | D | I | Z | C | |

| 0 | . | . | . | . | . | Z | C | |

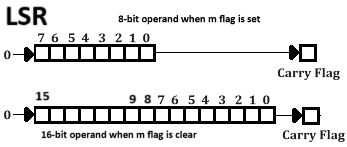

LSR (Logical Shift Right) is a 65x instruction that shifts every bit of a value one bit to the right (division by two). The most significant bit and negative flag are cleared. The least significant bit is shifted into the carry flag. The previous value of the carry flag is lost (unlike with ROR).

The size of the accumulator determines how many bits are shifted (8 or 16) not including the clearing zero and carry flag.

Syntax

LSR LSR A LSR addr LSR dp LSR addr, X LSR dp, X

Cycle Penalties

- Except in accumulator addressing, LSR takes an extra two cycles when the accumulator is 16 bits wide

- In direct page addressing modes, LSR takes another extra cycle if the low byte of the direct page register is nonzero.

See Also

External Links

- Eyes & Lichty, page 465 on LSR

- lbid page 191, before & after diagram of LSR

- Labiak, page 152 on LSR

- 10.1 on MCS6500 Manual, page 148 on LSR

- Carr, page 265 on LSR

- Leventhal, page 3-76 on LSR

- snes9x implementation of LSR: https://github.com/snes9xgit/snes9x/blob/master/cpuops.cpp#L862

- undisbeliever on LSR: https://undisbeliever.net/snesdev/65816-opcodes.html#lsr-logical-shift-right

- Pickens, John. http://www.6502.org/tutorials/6502opcodes.html#LSR

- Clark, Bruce. http://www.6502.org/tutorials/65c816opcodes.html#6.1.3