We've just updated MediaWiki and its underlying software. If anything doesn't look or work quite right, please mention it to us. --RanAS

ROR: Difference between revisions

From SnesLab

(using '816 version of image) |

(grammar improvement) |

||

| (16 intermediate revisions by the same user not shown) | |||

| Line 45: | Line 45: | ||

|[[C Flag|C]] | |[[C Flag|C]] | ||

|+ | |+ | ||

| | |N | ||

|. | |. | ||

|. | |. | ||

| Line 51: | Line 51: | ||

|. | |. | ||

|. | |. | ||

| | |Z | ||

| | |C | ||

|} | |} | ||

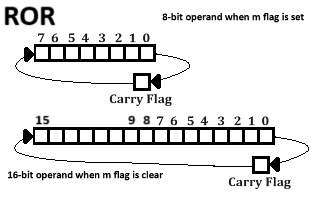

'''ROR''' (Rotate Right) is a 65x instruction that rotates a value and the [[carry flag]] right one bit. The least significant bit is shifted into the carry flag. The carry flag is shifted into the most significant bit. | '''ROR''' (Rotate Right) is a 65x instruction that rotates a value and the [[carry flag]] right one bit. The least significant bit is shifted into the carry flag. The carry flag is shifted into the most significant bit. | ||

When the accumulator is 8 bits wide, 9 bits are rotated. | * When the [[accumulator]] is 8 bits wide, 9 bits are rotated. | ||

When the accumulator is 16 bits wide, 17 bits are rotated. | * When the accumulator is 16 bits wide, 17 bits are rotated. | ||

==== Syntax ==== | ==== Syntax ==== | ||

| Line 70: | Line 70: | ||

</pre> | </pre> | ||

==== Cycle Penalties ==== | |||

* Except in [[accumulator addressing]], ROR takes two extra cycles when the accumulator is 16 bits wide. | * Except in [[accumulator addressing]], ROR takes two extra cycles when the accumulator is 16 bits wide. | ||

* In [[direct page addressing]] modes, ROR takes another extra cycle if the low byte of the [[direct page register]] is nonzero. | * In [[direct page addressing]] modes, ROR takes another extra cycle if the low byte of the [[direct page register]] is nonzero. | ||

[[File:816_ror.png]] | [[File:816_ror.png]] | ||

ROR was originally broken and so was left out of the earliest 6502 datasheets before it was fixed. It is available on 65x processors manufactured after June 1976. | |||

The arrow in the Carr textbook diagram does not circle back around. | |||

=== See Also === | === See Also === | ||

* [[ROL]] | * [[ROL]] | ||

* [[LSR]] | |||

* [[ROR (SPC700)]] | * [[ROR (SPC700)]] | ||

* [[ROR (Super FX)]] | * [[ROR (Super FX)]] | ||

=== External Links === | === External Links === | ||

* [[Eyes & Lichty]] | * [[Eyes & Lichty]], [https://archive.org/details/0893037893ProgrammingThe65816/page/491 page 491] on ROR | ||

* lbid, | * lbid, [https://archive.org/details/0893037893ProgrammingThe65816/page/191 page 191], before & after diagram on ROR | ||

* [[Labiak]] | * [[Labiak]], [https://archive.org/details/Programming_the_65816/page/n185 page 175] on ROR | ||

* [[MCS6500 Manual]] | * 10.4 on [[MCS6500 Manual]], [https://archive.org/details/mos_microcomputers_programming_manual/page/n171 page 150] on ROR | ||

* [[Carr]] | * [[Carr]], [https://archive.org/details/6502UsersManual/page/n282 page 269] on ROR | ||

* [[Leventhal]] | * [[Leventhal]], [https://archive.org/details/6502-assembly-language-programming/page/n136 page 3-87] on ROR | ||

* snes9x implementation of ROR: https://github.com/snes9xgit/snes9x/blob/master/cpuops.cpp#L1070 | * snes9x implementation of ROR: https://github.com/snes9xgit/snes9x/blob/master/cpuops.cpp#L1070 | ||

* undisbeliever on ROR: https://undisbeliever.net/snesdev/65816-opcodes.html#ror-rotate-right | * undisbeliever on ROR: https://undisbeliever.net/snesdev/65816-opcodes.html#ror-rotate-right | ||

* Pickens, John. http://www.6502.org/tutorials/6502opcodes.html#ROR | |||

* Clark, Bruce. http://www.6502.org/tutorials/65c816opcodes.html#6.1.3 | |||

[[Category:ASM]] | [[Category:ASM]] | ||

Latest revision as of 03:51, 20 September 2024

| Basic Info | |||||||

|---|---|---|---|---|---|---|---|

| Addressing Mode | Opcode | Length | Speed | ||||

| Accumulator | 6A | 1 byte | 2 cycles | ||||

| Absolute | 6E | 3 bytes | 6 cycles* | ||||

| Direct Page | 66 | 2 bytes | 5 cycles* | ||||

| Absolute Indexed by X | 7E | 3 bytes | 7 cycles* | ||||

| Direct Page Indexed by X | 76 | 2 bytes | 6 cycles* | ||||

| Flags Affected | ||||||||

|---|---|---|---|---|---|---|---|---|

| N | V | M | X | D | I | Z | C | |

| N | . | . | . | . | . | Z | C | |

ROR (Rotate Right) is a 65x instruction that rotates a value and the carry flag right one bit. The least significant bit is shifted into the carry flag. The carry flag is shifted into the most significant bit.

- When the accumulator is 8 bits wide, 9 bits are rotated.

- When the accumulator is 16 bits wide, 17 bits are rotated.

Syntax

ROR ROR A ROR addr ROR dp ROR addr, X ROR dp, X

Cycle Penalties

- Except in accumulator addressing, ROR takes two extra cycles when the accumulator is 16 bits wide.

- In direct page addressing modes, ROR takes another extra cycle if the low byte of the direct page register is nonzero.

ROR was originally broken and so was left out of the earliest 6502 datasheets before it was fixed. It is available on 65x processors manufactured after June 1976.

The arrow in the Carr textbook diagram does not circle back around.

See Also

External Links

- Eyes & Lichty, page 491 on ROR

- lbid, page 191, before & after diagram on ROR

- Labiak, page 175 on ROR

- 10.4 on MCS6500 Manual, page 150 on ROR

- Carr, page 269 on ROR

- Leventhal, page 3-87 on ROR

- snes9x implementation of ROR: https://github.com/snes9xgit/snes9x/blob/master/cpuops.cpp#L1070

- undisbeliever on ROR: https://undisbeliever.net/snesdev/65816-opcodes.html#ror-rotate-right

- Pickens, John. http://www.6502.org/tutorials/6502opcodes.html#ROR

- Clark, Bruce. http://www.6502.org/tutorials/65c816opcodes.html#6.1.3