We've just updated MediaWiki and its underlying software. If anything doesn't look or work quite right, please mention it to us. --RanAS

IBT: Difference between revisions

From SnesLab

(→References: hid archive URL) |

(added image) |

||

| (22 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

{| class="wikitable" style="float:right;clear:right;width:50%" | |||

{| class="wikitable" style="float:right;clear:right;width: | |||

!colspan="8"|Basic Info | !colspan="8"|Basic Info | ||

|+ | |+ | ||

|'''Addressing Mode''' | |||

|'''Opcode''' | |'''Opcode''' | ||

|'''Length''' | |'''Length''' | ||

| Line 10: | Line 9: | ||

|'''Cache Speed''' | |'''Cache Speed''' | ||

|+ | |+ | ||

|[[Immediate]] | |||

|Anpp | |Anpp | ||

|2 bytes | |2 bytes | ||

| Line 18: | Line 18: | ||

{| class="wikitable" style="float:right;clear:right;width:30%" | {| class="wikitable" style="float:right;clear:right;width:30%" | ||

!colspan="9"|Flags | !colspan="9"|Flags Affected | ||

|+ | |+ | ||

|B | |[[B Flag|B]] | ||

|ALT1 | |[[ALT1]] | ||

|ALT2 | |[[ALT2]] | ||

|O/V | |[[O/V]] | ||

|S | |[[Sign Flag|S]] | ||

|CY | |[[CY]] | ||

|Z | |[[Zero Flag|Z]] | ||

|+ | |+ | ||

|0 | |0 | ||

| Line 36: | Line 36: | ||

|. | |. | ||

|} | |} | ||

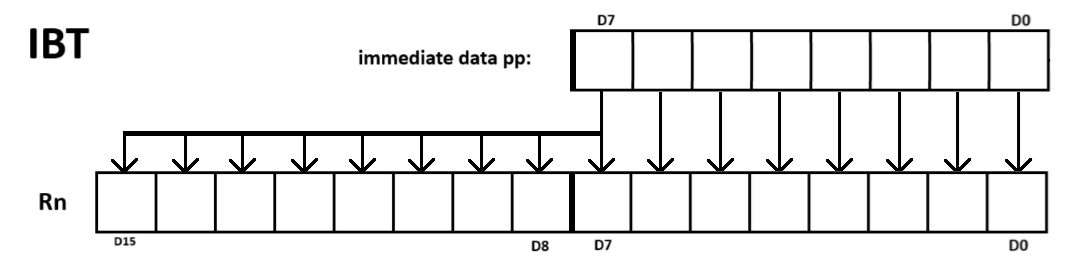

'''IBT''' (Immediate Byte Transfer) is a [[Super FX]] instruction that loads an immediate byte into the low byte of a specified general register. The register's upper eight bits will be sign-extended (copied) from bit 7, effectively loading a signed 8-bit value. | |||

The [[ALT0]] state is restored. | |||

==== Syntax ==== | |||

<pre> | |||

IBT Rn, #pp | |||

</pre> | |||

where pp may be from -128 to 127. Any of the 16 general registers can be specified. | |||

==== Example ==== | |||

IBT R<sub>8</sub>, #4 ; 0004h -> R<sub>8</sub> | |||

IBT R<sub>8</sub>, #-128 ; ff80h -> R<sub>8</sub> | |||

IBT R<sub>8</sub>, #0A4h ; ffa4h -> R<sub>8</sub> | |||

==== Trivia ==== | |||

The word "integer" is misspelled in the official manual page for IBT. | |||

[[File:ibt.png]] | |||

=== See Also === | === See Also === | ||

* [[IWT]] | * [[IWT]] | ||

* [[LDA]] | * [[LDA]] | ||

* [[LDX]] | |||

* [[LDY]] | |||

=== External Links === | === External Links === | ||

* Official Nintendo documentation on IBT: [https://archive.org/details/SNESDevManual/book2/page/ | * Official Nintendo documentation on IBT: 9.41 on [https://archive.org/details/SNESDevManual/book2/page/n216 Page 2-9-60 of Book II] | ||

[[Category:ASM]] | [[Category:ASM]] | ||

[[Category:Super FX]] | [[Category:Super FX]] | ||

[[Category:GSU_Control_Instructions]] | [[Category:GSU_Control_Instructions]] | ||

[[Category:Two-byte Instructions]] | |||

Latest revision as of 02:24, 16 July 2024

| Basic Info | |||||||

|---|---|---|---|---|---|---|---|

| Addressing Mode | Opcode | Length | ROM Speed | RAM Speed | Cache Speed | ||

| Immediate | Anpp | 2 bytes | 6 cycles | 6 cycles | 2 cycles | ||

| Flags Affected | ||||||||

|---|---|---|---|---|---|---|---|---|

| B | ALT1 | ALT2 | O/V | S | CY | Z | ||

| 0 | 0 | 0 | . | . | . | . | ||

IBT (Immediate Byte Transfer) is a Super FX instruction that loads an immediate byte into the low byte of a specified general register. The register's upper eight bits will be sign-extended (copied) from bit 7, effectively loading a signed 8-bit value.

The ALT0 state is restored.

Syntax

IBT Rn, #pp

where pp may be from -128 to 127. Any of the 16 general registers can be specified.

Example

IBT R8, #4 ; 0004h -> R8 IBT R8, #-128 ; ff80h -> R8 IBT R8, #0A4h ; ffa4h -> R8

Trivia

The word "integer" is misspelled in the official manual page for IBT.

See Also

External Links

- Official Nintendo documentation on IBT: 9.41 on Page 2-9-60 of Book II