We've just updated MediaWiki and its underlying software. If anything doesn't look or work quite right, please mention it to us. --RanAS

Master Clock: Difference between revisions

From SnesLab

(→See Also: FastROM, SlowROM) |

(→See Also: machine cycle) |

||

| Line 8: | Line 8: | ||

* [[FastROM]] | * [[FastROM]] | ||

* [[SlowROM]] | * [[SlowROM]] | ||

* [[Machine Cycle]] | |||

=== Reference === | === Reference === | ||

Revision as of 02:52, 17 August 2024

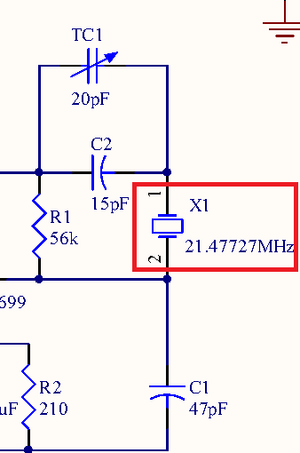

The Master Clock is 21.48 MHz on NTSC and 21.28 MHz on PAL.

The master clock (X1) is in region A4 of the jwdonal schematic