S-DSP: Difference between revisions

(linkify OUTX) |

(note about pin 47) |

||

| (5 intermediate revisions by the same user not shown) | |||

| Line 30: | Line 30: | ||

| || | | || | ||

|- | |- | ||

| 0C || MVOL (L) | | 0C || [[MVOL]] (L) | ||

|- | |- | ||

| 1C || MVOL (R) | | 1C || [[MVOL]] (R) | ||

|- | |- | ||

| 2C || EVOL (L) | | 2C || EVOL (L) | ||

| Line 46: | Line 46: | ||

| 7C || ∴[[ENDX]] | | 7C || ∴[[ENDX]] | ||

|- | |- | ||

| 0D || EFB | | 0D || [[EFB]] | ||

|- | |- | ||

| 1D || --- | | 1D || --- | ||

| Line 52: | Line 52: | ||

| 2D || [[PMON]] | | 2D || [[PMON]] | ||

|- | |- | ||

| 3D || NON | | 3D || [[NON]] | ||

|- | |- | ||

| 4D || EON | | 4D || [[EON]] | ||

|- | |- | ||

| 5D || [[DIR]] | | 5D || [[DIR]] | ||

|- | |- | ||

| 6D || ESA | | 6D || [[ESA]] | ||

|- | |- | ||

| 7D || EDL | | 7D || [[EDL]] | ||

|- | |- | ||

| xE || --- | | xE || --- | ||

| Line 66: | Line 66: | ||

Many of the 128 registers appear to not be used by the S-DSP directly, but get copied to internal registers the S-SMP does not have access to. The highest sound frequency that the S-DSP can produce is 16kHz, because of the 32kHz rate that sample-points are output. <sup>[1]</sup> | Many of the 128 registers appear to not be used by the S-DSP directly, but get copied to internal registers the S-SMP does not have access to. The highest sound frequency that the S-DSP can produce is 16kHz, because of the 32kHz rate that sample-points are output. <sup>[1]</sup> | ||

The arrowhead for pin 47 on the jwdonal schematic seems to be pointing the wrong way. | |||

=== References === | === References === | ||

# https://problemkaputt.de/fullsnes.htm#snesapudspbrrpitch | # https://problemkaputt.de/fullsnes.htm#snesapudspbrrpitch | ||

# [https://archive.org/details/SNESDevManual/book1/page/n167 page 3-7-1 of Book | # [https://archive.org/details/SNESDevManual/book1/page/n167 page 3-7-1 of Book I] of the official Super Nintendo development manual | ||

# subparagraph 22.5.2 on [https://archive.org/details/SNESDevManual/book1/page/n97 page 2-22-1 of Book I], lbid. | |||

[[Category:SNES Hardware]] | [[Category:SNES Hardware]] | ||

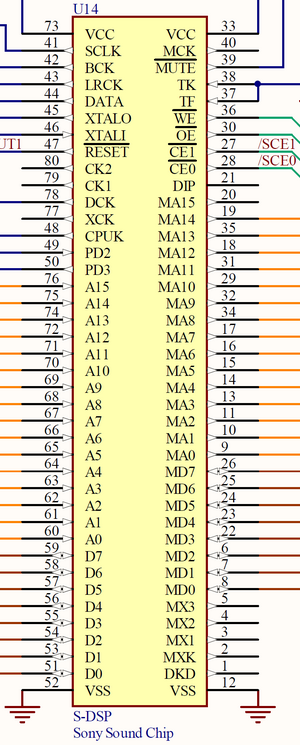

Latest revision as of 20:35, 18 August 2024

The S-DSP is the digital signal processor. It produces audio for the DAC and is controlled by the S-SMP. It is clocked by X2.

It has 128 registers (DSPRAM) that can be manipulated by the S-SMP, some of which serve no hard-wired purpose and can be used as general-purpose RAM. Registers with a ∴ before their name are written to by the S-DSP itself during active processing. Here are some of 128:

| Address | Register |

|---|---|

| 00 | VOL (L) |

| 01 | VOL (R) |

| 02 | P (L) |

| 03 | P (H) |

| 04 | SRCN |

| 05 | ADSR (1) |

| 06 | ADSR (2) |

| 07 | GAIN |

| 08 | ∴ENVX |

| 09 | ∴OUTX |

| 0C | MVOL (L) |

| 1C | MVOL (R) |

| 2C | EVOL (L) |

| 3C | EVOL (R) |

| 4C | KON |

| 5C | KOF |

| 6C | FLG |

| 7C | ∴ENDX |

| 0D | EFB |

| 1D | --- |

| 2D | PMON |

| 3D | NON |

| 4D | EON |

| 5D | DIR |

| 6D | ESA |

| 7D | EDL |

| xE | --- |

Many of the 128 registers appear to not be used by the S-DSP directly, but get copied to internal registers the S-SMP does not have access to. The highest sound frequency that the S-DSP can produce is 16kHz, because of the 32kHz rate that sample-points are output. [1]

The arrowhead for pin 47 on the jwdonal schematic seems to be pointing the wrong way.

References

- https://problemkaputt.de/fullsnes.htm#snesapudspbrrpitch

- page 3-7-1 of Book I of the official Super Nintendo development manual

- subparagraph 22.5.2 on page 2-22-1 of Book I, lbid.