We've just updated MediaWiki and its underlying software. If anything doesn't look or work quite right, please mention it to us. --RanAS

Audio RAM: Difference between revisions

From SnesLab

(→See Also: ARAM Write Enable Flag) |

(power up value) |

||

| (One intermediate revision by the same user not shown) | |||

| Line 2: | Line 2: | ||

There are two '''ARAM''' chips on the [[SNES Motherboard]], both connected to [[S-DSP]]. All accesses from the [[SPC700]] go through the S-DSP. ARAM is a total of 65,536 bytes (or 256 pages, or one [[bank]], or 512 [[kilobits]]) in size. ARAM is timeshared between the S-SMP and S-DSP. | There are two '''ARAM''' chips on the [[SNES Motherboard]], both connected to [[S-DSP]]. All accesses from the [[SPC700]] go through the S-DSP. ARAM is a total of 65,536 bytes (or 256 pages, or one [[bank]], or 512 [[kilobits]]) in size. ARAM is timeshared between the S-SMP and S-DSP. | ||

According to [[fullsnes]], ARAMs consisting of two Motorola MCM51L832F12 32Kx8 SRAM chips tend to contain a repeating 64-byte pattern of 32 zeros and then 32 FFh's at power up. | |||

=== See Also === | === See Also === | ||

| Line 7: | Line 9: | ||

* [[VRAM]] | * [[VRAM]] | ||

* [[ARAM Write Enable Flag]] | * [[ARAM Write Enable Flag]] | ||

* [[Uppermost Page]] | |||

=== References === | === References === | ||

Latest revision as of 00:53, 14 August 2024

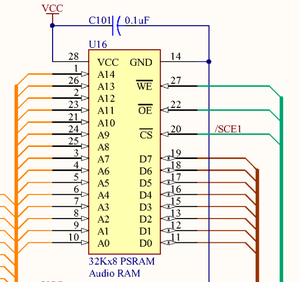

upper ARAM chip, straddling regions C4 and D4 of the jwdonal schematic

There are two ARAM chips on the SNES Motherboard, both connected to S-DSP. All accesses from the SPC700 go through the S-DSP. ARAM is a total of 65,536 bytes (or 256 pages, or one bank, or 512 kilobits) in size. ARAM is timeshared between the S-SMP and S-DSP.

According to fullsnes, ARAMs consisting of two Motorola MCM51L832F12 32Kx8 SRAM chips tend to contain a repeating 64-byte pattern of 32 zeros and then 32 FFh's at power up.

See Also

References

- subparagraph 22.5.3 on Page 2-22-3 of Book I of the official Super Nintendo development manual

- subparagraph 1.3.3 on page 3-1-2 of Book I, lbid.