We've just updated MediaWiki and its underlying software. If anything doesn't look or work quite right, please mention it to us. --RanAS

Address Bus B: Difference between revisions

From SnesLab

(which chip it's connected to is more important) |

(note about address decoder) |

||

| Line 9: | Line 9: | ||

* [[Expansion Port]] pins 1-8 | * [[Expansion Port]] pins 1-8 | ||

which is the exact same set of components that the [[CPU Data Bus]] is connected to. The SNES bus is drawn in purple in the colorized [[jwdonal schematic]]. Some people like to think of Address Bus B as being 16-bits wide, with the high byte being fixed to $21.<sup>[1]</sup> | which is the exact same set of components that the [[CPU Data Bus]] is connected to. The SNES bus is drawn in purple in the colorized [[jwdonal schematic]]. Some people like to think of Address Bus B as being 16-bits wide, with the high byte being fixed to $21.<sup>[1]</sup> An address decoder translates the 65c816's bus addresses into SNES bus addresses.<sup>[4]</sup> | ||

[[File:SNES Bus.png|thumb]] | [[File:SNES Bus.png|thumb]] | ||

| Line 20: | Line 20: | ||

# Figure 2-22-1, "Super NES Functional Block Diagram" on [https://archive.org/details/SNESDevManual/book1/page/n98 page 2-22-2 of Book I] | # Figure 2-22-1, "Super NES Functional Block Diagram" on [https://archive.org/details/SNESDevManual/book1/page/n98 page 2-22-2 of Book I] | ||

# paragraph 3.2 on [https://archive.org/details/SNESDevManual/book1/page/n160 page 3-3-2 of Book I], lbid. | # paragraph 3.2 on [https://archive.org/details/SNESDevManual/book1/page/n160 page 3-3-2 of Book I], lbid. | ||

# https://forums.nesdev.org/viewtopic.php?p=195152#p195152 | |||

[[Category:SNES Hardware]] | [[Category:SNES Hardware]] | ||

[[Category:Traces]] | [[Category:Traces]] | ||

[[Category:Buses]] | [[Category:Buses]] | ||

Revision as of 20:25, 17 August 2024

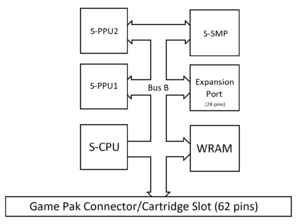

Address Bus B, also known as the SNES bus, is 8-bits wide on the SNES Motherboard. Its individual address lines are labeled PA0-PA7, which stands for "peripheral address," as in S-CPU peripherals (not SNES peripherals). It is connected to:

- S-CPU pins 51-58

- S-PPU1 pins 5-12

- S-PPU2 pins 17-24

- S-SMP pins 48-51

- WRAM pins 43-50 and 53-54

- Cartridge Slot pins 28-30 and 59-61, 3 and 34

- Expansion Port pins 1-8

which is the exact same set of components that the CPU Data Bus is connected to. The SNES bus is drawn in purple in the colorized jwdonal schematic. Some people like to think of Address Bus B as being 16-bits wide, with the high byte being fixed to $21.[1] An address decoder translates the 65c816's bus addresses into SNES bus addresses.[4]

See Also

References

- https://forums.nesdev.org/viewtopic.php?p=116505#p116505

- Figure 2-22-1, "Super NES Functional Block Diagram" on page 2-22-2 of Book I

- paragraph 3.2 on page 3-3-2 of Book I, lbid.

- https://forums.nesdev.org/viewtopic.php?p=195152#p195152